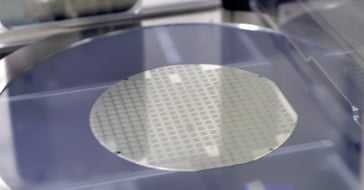

Garantia de suporte a componentes de longo prazo para projetos existentes com armazenamento de wafers

Na primeira parte de nossa exploração do quebra-cabeça da fabricação, analisamos o histórico de como e por que as montagens de semicondutores se afastaram da montagem clássica de arranjo de terminais. Para recapitular, elas requerem caras ferramentas de recorte e forma e o mercado adotou montagens dos tipos BGA (Matriz de grade de esferas), QFN (Encapsulamento quadrado fino sem terminais) ou DFN (Encapsulamento duplo fino sem terminais) com base em substratos. Na segunda parte, discutimos como montagens QFN e DFN, que estão na ponta inferior de complexidade e custo, terão alto impacto no futuro de montagens SOIC e PLCC de baixa contagem de pinos. Agora, na terceira parte, voltamos o nosso foco para tecnologias de armazenamento de wafers e de fabricação de semicondutores.

O que impulsiona a demanda por armazenamento de wafers e ela está sempre disponível?

Como acontece com muitos desafios tecnológicos, a resposta é complicada e, para compreender as sutilezas dela, temos de entrar em detalhes.

O argumento em favor do armazenamento de wafers é bem simples e consiste em duas ideias. Primeiramente, evita-se custos de montagem e ensaio quando o processo de fabricação é descontinuado. Em segundo lugar, wafers podem ser armazenados em menos espaço e por mais tempo do que produtos montados. Ambos os aspectos são verdadeiros, especialmente em relação a produtos mais antigos, mas apenas desde que:

- A montagem e o ensaio ainda possam ser realizados.

- O estado do produto de wafer seja totalmente testado e/ou configurado.

A primeira condição pode parecer óbvia, mas muitos ignoram o significado em potencial. A montagem ou o encapsulamento precisa permanecer disponível para que o armazenamento de wafers continue a fazer sentido. A viabilidade da plataforma de ensaio deve persistir enquanto o armazenamento de wafers for necessário. Em nossos artigos anteriores sobre o quebra-cabeça da fabricação, discutimos encapsulamentos e como as tecnologias clássicas de arranjo de terminais estão sendo abandonadas. Plataformas de testadores e circuitos externos apropriados devem estar disponíveis por toda a duração desejada do armazenamento de wafers. Se a disponibilidade de testadores não puder ser garantida, a portabilidade de programas de ensaios é outro custo considerado para determinar a viabilidade financeira do armazenamento de wafers. Essa primeira condição pode ser superada com planejamento e preparação adequados. A Rochester Electronics tem investido em montagem e ensaios para continuar a viabilizar o armazenamento de wafers.

A segunda parte do argumento sobre a necessidade de produtos de wafer serem totalmente testados e/ou configurados é muito mais complicada. No último meio século de armazenamento de wafers no setor de semicondutores, foi fácil compreender a complexidade dos produtos e que ensaios e montagem garantiram a viabilidade. Hoje, isso é muito menos simples. Diversos fatores aumentam a complexidade do estado de produtos de wafer, incluindo:

- Produtos de memória que são commodities não existem isoladamente. Como os custos de máscaras de nós avançadas são muito altos, está se tornando comum que um único conjunto de máscaras represente vários produtos selecionados de operação de fusíveis para classificação de wafers. Não é incomum que o mesmo wafer represente de 4 a 8 produtos finais diferentes.

- Conhecer a posição no inventário de qualquer um dos produtos individualmente não é algo claro com wafers multiproduto.

- Memórias EEPROM geralmente requerem uma operação de classificação de wafers em alta temperatura antes da montagem. Isso significa que um programa de ensaio de classificação de wafers deve fazer parte do processo de armazenamento de wafers.

- Produtos com memória grande integrada são forçados a implementar BISR (Autorreparo integrado) para que haja uma operação de classificação de wafers. Isso ocorre para a maioria das tecnologias em 65 nm e abaixo, em que a área do chip é principalmente memória. O BISR é executado como uma operação de classificação de wafers, normalmente seguida de fusão para permitir que colunas ou linhas de memória redundantes sejam alternadas e melhorem o rendimento. Os algoritmos de BISR são proprietários e exclusivos de cada empresa de semicondutores ou provedor de propriedade intelectual.

- É necessário realizar o bump de produtos de wafer que sejam do tipo chip virado para que eles possam ser montados. A metalurgia de bump é importante e ainda não está claro se bumps com qualquer teor de chumbo geram preocupações de confiabilidade de longo prazo. Mais estudos precisam ser feitos. O armazenamento de wafers poderia ser feito sem bump, mas daí as operações de BISR e fusão precisariam ser ocorrer ao longo do tempo.

- Se um produto de wafer estiver em uma montagem BGA, será necessário ter um substrato disponível para que o chip seja ligado ou o chip virado seja montado. Substratos não têm longo prazo de vida útil e devem ser adquiridos em quantidades por pedido que geralmente excedem a demanda de longo prazo do sistema. O armazenamento de longo prazo de substratos é algo que também precisa de mais estudos.

Respondendo o que impulsiona o armazenamento de wafers e se ele está sempre disponível, a verdadeira resposta é que depende do produto. Todas as condições examinadas acima precisam ser compreendidas para a avaliação final de viabilidade.

Quando wafers estão disponíveis em um evento de LTB (Última compra)?

A realidade é que a disponibilidade de armazenamento de wafers nem sempre é uma opção apresentada aos clientes finais. As expectativas financeiras de uma LTB são para produtos acabados e um aumento de curto prazo na receita antes do encerramento do evento de LTB. Há uma resistência inerente a se contentar com menos receita do que produtos acabados para eventos de LTB. O evento já estará previsto e a receita está planejada. Isso deve fazer parte do plano de negócios antes do evento. Empresas de semicondutores sem fábrica têm uma cadeia de suprimentos externa para a maioria dos produtos. A fabricação, montagem e os ensaios de semicondutores são, em sua maioria, itens subcontratados. Elas normalmente não têm um ponto de saída em seu fluxo de fabricação de produtos apenas para wafers. Em suma, a maioria das empresas de semicondutores sem fábrica não identificou apenas wafers como um item de desenvolvimento ou uma entrega.

As discussões sobre armazenamento de wafers com uma empresa de semicondutores sem fábrica devem ocorrer antes do evento de LTB ou as chances de se ter um armazenamento adequado são drasticamente reduzidas. Os IDMs (Fabricantes de dispositivos integrados) que têm as próprias instalações de fabricação podem fazer as coisas de forma diferente. IDMs têm mais controle sobre cada etapa de seu fluxo de desenvolvimento de produtos. IDMs estão mais propensos a fazer uma compra de wafers do que empresas sem fábrica, mas essa discussão deve acontecer antes de um evento de LTB ou a chance pode ser perdida.

A disponibilidade de wafers em um evento de LTB é complicada e rara. As chances de aquisição após um evento de LTB ser anunciado são baixas. Planejamento adequado por parte de equipes de gestão de produtos e empresas como a Rochester Electronics aumenta as chances de implementar com sucesso um contrato de armazenamento de wafers de longo prazo. A Rochester Electronics tem bilhões de chips em armazenamento e continua a aumentar sua seleção de produtos para oferecer a clientes de sistemas de longo prazo os produtos totalmente autorizados necessários para décadas de vida útil de sistemas. Além disso, a Rochester determinou que um produto pode ser armazenado por décadas, garantindo o suprimento para os clientes.

Como fabricante licenciada de semicondutores, a Rochester já fabricou mais de 20 000 tipos de dispositivo. Com mais de 12 bilhões de chips em estoque, a Rochester tem a capacidade para fabricar mais de 70 000 tipos de dispositivo.

Há mais de 40 anos, em parceria com mais de 70 dentre os principais fabricantes de semicondutores, a Rochester fornece aos nossos prezados clientes uma fonte contínua de semicondutores críticos.

A Rochester Electronics oferece uma variedade de serviços nas suas instalações de Newburyport para prolongar a vida útil de produtos semicondutores com serviços de armazenamento de wafers e processamento de chips.

Processamento de wafer

- Afinamento de wafer

- Corte de wafer

- Coleta e colocação de chip

- Inspeção do chip

Armazenamento de chip

Armazenamento a longo prazo

- Programas de armazenamento a longo prazo e de fabricação com logística gerenciada

- Aceitação de lote e serviços de ensaio de confiabilidade para garantir a funcionalidade total do produto

- Gerenciamento de peças

- Relatórios de uso

- Documentos associados são convertidos e armazenados eletronicamente

- Controle de ERP do inventário e dos atributos de wafers

- Geração de mapa eletrônico de wafer para wafers marcados com tinta

Armazenamento de última geração

- Certificado ISO-7/10K

- Controles ESD aprimorados

- Áreas de inspeção ISO-5

- Controle de umidade relativa

- Monitoramento em tempo real de temperatura e umidade

- Purga automática em falha de energia

- Sala segura e gabinetes individuais

Deseja saber mais? Entre em contato conosco hoje.

Saiba mais sobre as soluções de processamento e armazenamento de wafers da Rochester

ASSISTA: para explorar os nossos recursos de processamento e armazenamento de wafers